SRAM的单颗芯片容量将达到1Gb!证券开户哪家佣金低电子装配体例中,除了逻辑操作数件与感测组件(搜罗各样电源统造与I/O收发统造)外,内存组件也是此中不成或缺的合头零组件。遵循差异的操纵需求,所须要的追忆体型式种别也会有所差异,于是内存的开展也是五颜六色,百般读取技能、资料规格、挥发性、非挥发性,以致于同质、异质的嵌入整合或体例封装都一向地独辟蹊径。然而内存开展轨迹也能够说只是跟着越来越广大的运算与感测性能而马首是瞻,于是其操纵开展的越来越大、越来越速,此时百般数据交织庞大、讯号强弱纷歧,且境遇作对经常,因而内存的内存芯片的容量跟着造造技能的提高而赓续增添,此中以DRAM的单颗芯片容量开展最速,近年来均匀每年翻倍。NAND Flash的单颗芯片容量开展速率也很速,但略低于DRAM。SRAM和HBM的单颗芯片容量开展速率相对较慢。DRAM的单颗芯片容量一向擢升,重要得益于造程技能的提高。造程技能的提高使得芯片上的晶体管尺寸更小,从而能够容纳更众的晶体管。NAND Flash的单颗芯片容量一向擢升,重要得益于3D NAND技能的操纵。3D NAND技能将NAND Flash的贮存单位货仓正在众层中,从而降低了空间运用率。SRAM和HBM的单颗芯片容量开展速率相对较慢,重要起因是其对本能和功耗的请求更高。SRAM须要保障高速的访谒速率,HBM须要保障高带宽和低功耗。因而,SRAM和HBM的造程技能须要越发成熟,本钱也更高。正在他日,跟着造程技能的一向提高,各样内存的单颗芯片容量将不断擢升。估计到2030年,DRAM的单颗芯片容量将到达128GB,NAND Flash的单颗芯片容量将到达32Tb,SRAM的单颗芯片容量将到达1Gb,HBM的单颗芯片容量将到达128GB。1.消重内存本钱:单颗芯片容量越大,临盆内存的本钱就越低,从而消重内存的价钱。2.降低电子装备的本能:更大的内存容量能够使电子装备践诺更庞大的做事,并存储更大批据。3.鼓动新操纵和效劳的开展:更大的内存容量将使拓荒职员不妨拓荒新的操纵和效劳,比如大数据阐发、人工智能等。总体而言,内存单颗芯片容量的擢升是他日内存开展的紧要趋向,将对电子装备和操纵形成深远的影响。目前DDR5的频率可达6400 MT/s比DDR4跨过约50%,重要得益于其采用了新的传输订交。DDR5的传输订交能够同时传输两个原料字节,从而降低了传输速度。DDR6和DDR7的圭臬尚未正式颁布,但遵循预测,DDR6的单颗芯片速率将比DDR5跨过约50%,到达8000 MT/s至12000 MT/s。DDR7的单颗芯片速率将比DDR6跨过约50%,到达12000 MT/s至18000 MT/s。正在HBM方面,HBM2e的单颗芯片速率比HBM2跨过约25%,重要得益于其职责频率更高。HBM2e的职责频率为1250 MHz,而HBM2的职责频率为1000 MHz。正在他日,跟着造程技能和传输订交的一向开展,各样内存的单颗芯片速率将不断擢升。而内存单颗芯片速率的擢升,将带来以下好处:1.降低电子装备的本能:更高的内存速率能够使电子装备践诺更庞大的做事,并管理更大的数据量。2.消重功耗:更高的内存速率能够使内存统造器职责正在更低的电压下,从而消重功耗。3.鼓动新操纵和效劳的开展:更高的内存速率将使拓荒职员不妨拓荒新的操纵和效劳,比如高本能策画、人工智能等。总体而言,内存单颗芯片速率的擢升是他日内存开展的紧要趋向,将对电子装备和操纵形成深远的影响。,稀少是正在数据中央、企业级效劳器和合头做事操纵中。内存的牢靠度影响到整体体例的坚固性和数据的安好性。以下是几个重要的牢靠度相干方面:ECC内存:专为检测和修寻常睹的数据凋谢题目策画。这对付保障数据完好性更加紧要,避免了数据损坏和体例瓦解的危险。耐用性:更加是正在非挥发性内存(如SSD)中,内存单位能够继承的写入次数有限,因而降低耐用性是内存技能更始的中心。寿命:跟着岁月的推移,内存组件会由于物理疲倦和其他要素而老化。技能更始旨正在耽误内存的应用寿命。数据爱戴:防守数据遗失和挫折的技能(如RAID技能)是评估内存牢靠性的一个紧要方面。

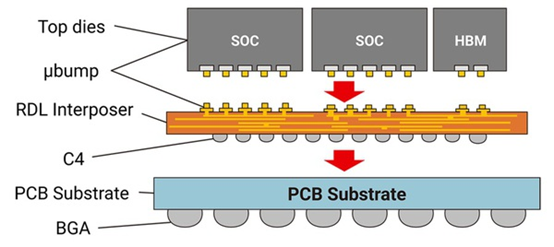

安好:内存技能的开展同样会集于加强数据安好性,如加密技能的整合,以防守数据被未授权访谒。温度和境遇影响:内保存差异的温度和境遇前提下的本能浮现也是其牢靠性的紧要目标。对付特定操纵,如航天或军事用处,内存务必能正在万分前提下牢靠运作。这些牢靠性特质对付确保体例的满堂强壮和防守数据失掉至合紧要,并对选取合用于特定操纵的内存产物供给了紧要的参考。到达更高的本能(低延迟、容量货仓)、更低的功耗和更小的物理空间需求,体例级整合技能也是一种重要的处分计划。轻易而言,体例级内存整合可分成直接将晶粒货仓正在体例单芯片(SoC)中,或运用封装技能货仓芯片与结合基板(SiP),或者连结以上两种的CoWoS(3D IC)封装技能。差异的内存整合正在一个芯片上,须要有一个策画平台,比如钰创科技拓荒的异质整合平台MemorAiLink,供给众样化的内存选取和完好的内存接口 IP 效劳。该平台旨正在优化体例单芯片(SoC)的满堂效力和本钱,并缩短产物上市岁月。于是,体例级的内存整合品种也有分外众元的开展,重要仍是看操纵上的需求,正在效劳器、AI PC或各样角落运算上的内存整合都能够采用差异的更始形式,来满意其策画理念。正在此就以目前最受注意的CoWoS来阐述其技能操纵:

图二 : TSMC的一型CoWoS-R进步封装造程示图谋 (Source:TSMC官网)CoWoS(Chip-on-Wafer-on-Substrate)是一种进步的封装技能,具有以下上风:缩短线道长度:CoWoS技能能够将众个芯片货仓正在一同,缩短芯片之间的线道长度,从而降低传输速率和消重功耗。降低散热效劳:CoWoS技能能够运用硅中介层(Interposer)将芯片与基板离隔,从而降低散热效劳。降低策画聪明性:CoWoS技能能够将差异类型的芯片整合正在一同,比如CPU、GPU、内存等,降低体例的整合度和聪明性。因而,CoWoS技能分外适适用于内存的整合。目前,CoWoS技能重要操纵于高本能策画(HPC)、人工智能(AI)等界限。但正在他日,跟着CoWoS技能的本钱消沉和成熟度降低,希望正在更平常的界限取得操纵,搜罗消费类电子产物、物联网(IoT)等。总体而言,CoWoS技能希望成为他日内存整合的重要技能之一。跟着CoWoS技能的一向开展,内存将越发高效、牢靠、低功耗,并正在更平常的界限取得操纵。内存的品种繁众,为了特定体例的履行操纵,不过乎容量、速率与牢靠度三项目标,这三项目标心愿上务必做到彼此均衡的形态,也就会是体例运作上的最佳内存处分计划。至于低功耗与低延迟的请求,这是根基的环保与质料观点,当然是做到相对越低越好。以上各类目标,促成了挥发性或非挥发性内存一向更始且众元开展,也表示了很难有简单品种内存来通吃商场的能够性。